- 您现在的位置:买卖IC网 > Sheet目录3858 > PIC18F26J50-I/ML (Microchip Technology)IC PIC MCU FLASH 64K 2V 28-QFN

2009 Microchip Technology Inc.

DS39687E-page 19

PIC18F2XJXX/4XJXX FAMILY

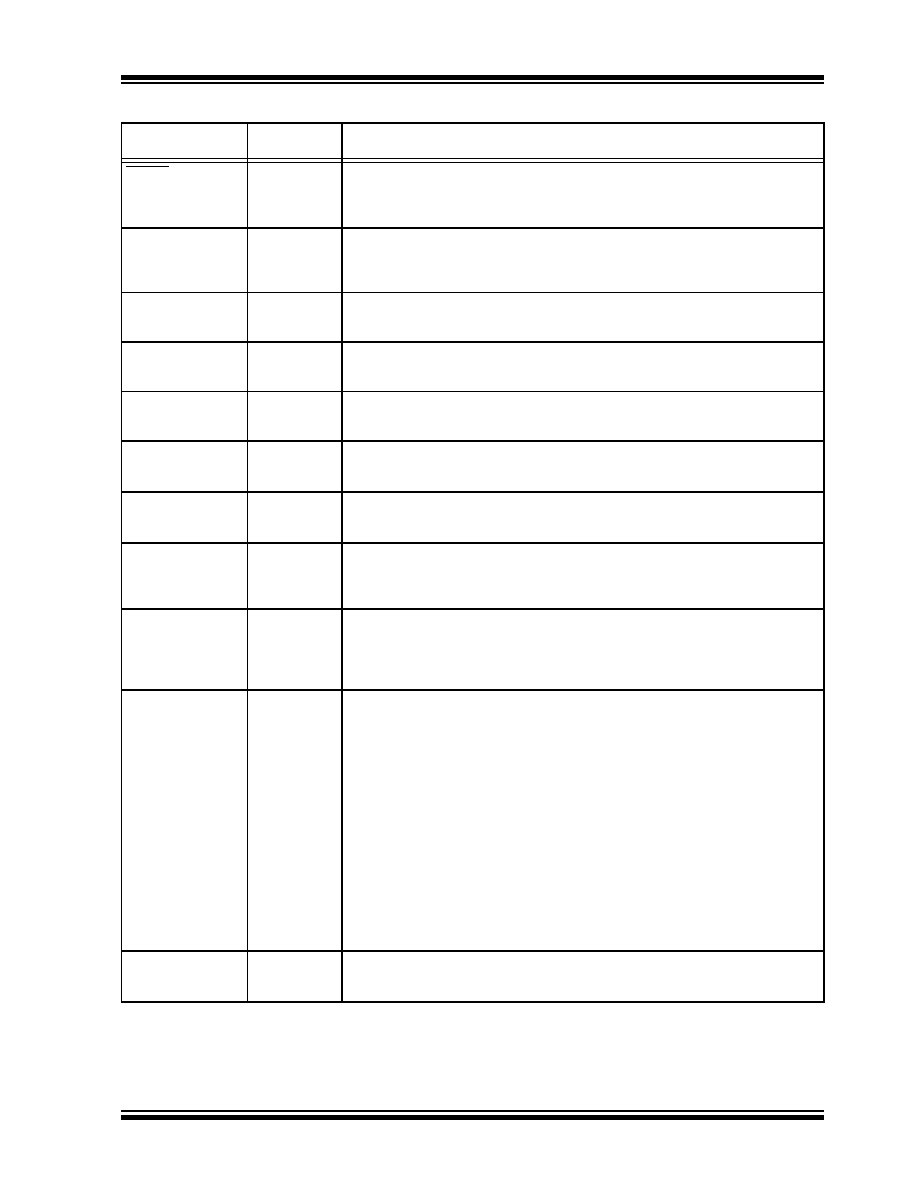

TABLE 5-3:

PIC18F45J10 FAMILY DEVICES: BIT DESCRIPTIONS

Bit Name

Configuration

Words

Description

DEBUG

CONFIG1L

Background Debugger Enable bit

1 = Background debugger disabled, RB6 and RB7 configured as general

purpose I/O pins

0 = Background debugger enabled, RB6 and RB7 are dedicated to in-circuit debug

XINST

CONFIG1L

Extended Instruction Set Enable bit

1 = Instruction set extension and Indexed Addressing mode enabled

0 = Instruction set extension and Indexed Addressing mode disabled

(Legacy mode)

STVREN

CONFIG1L

Stack Overflow/Underflow Reset Enable bit

1 = Reset on stack overflow/underflow enabled

0 = Reset on stack overflow/underflow disabled

WDTEN

CONFIG1L

Watchdog Timer Enable bit

1 = WDT enabled

0 = WDT disabled (control is placed on SWDTEN bit)

CP0

CONFIG1H

Code Protection bit

1 = Program memory is not code-protected

0 = Program memory is code-protected

IESO

CONFIG2L

Internal/External Oscillator Switchover bit

1 = Oscillator Switchover mode enabled

0 = Oscillator Switchover mode disabled

FCMEN

CONFIG2L

Fail-Safe Clock Monitor Enable bit

1 = Fail-Safe Clock Monitor enabled

0 = Fail-Safe Clock Monitor disabled

FOSC2

CONFIG2L

Default Oscillator Select bit

1 = Clock designated by FOSC<1:0> is enabled as system clock when

OSCCON<1:0> = 00

0 = INTRC is enabled as system clock when OSCCON<1:0> = 00

FOSC<1:0>

CONFIG2L

Primary Oscillator Select bits

11 = EC oscillator, PLL enabled and under software control, CLKO function on OSC2

10 = EC oscillator, CLKO function on OSC2

01 = HS oscillator, PLL enabled and under software control

00 = HS oscillator

WDTPS<3:0>

CONFIG2H

Watchdog Timer Postscale Select bits

1111 = 1:32,768

1110 = 1:16,384

1101 = 1:8,192

1100 = 1:4,096

1011 = 1:2,048

1010 = 1:1,024

1001 = 1:512

1000 = 1:256

0111 = 1:128

0110 = 1:64

0101 = 1:32

0100 = 1:16

0011 = 1:8

0010 = 1:4

0001 = 1:2

0000 = 1:1

CCP2MX

CONFIG3H

CCP2 MUX bit

1 = CCP2 is multiplexed with RC1

0 = CCP2 is multiplexed with RB3

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DSPIC33FJ64GP204-E/ML

IC DSPIC MCU/DSP 64K 44-QFN

PIC32MX130F064B-I/SP

IC MCU 32BIT 64KB FLASH 28-SPDIP

PIC18F1330-I/P

IC PIC MCU FLASH 4KX16 18DIP

ATTINY12-8PC

IC AVR MCU 1K 5V 8MHZ COM 8-DIP

ATTINY11L-2SI

IC AVR MCU 8-BIT FLSH LOW V SO-8

ATTINY11L-2SC

IC AVR MCU 8 BIT FLSH LOW V SO-8

PIC24HJ16GP304-I/PT

IC PIC MCU FLASH 16K 44TQFP

ATTINY12V-1SC

IC AVR MCU 1MHZ 1.8V SO-8

相关代理商/技术参数

PIC18F26J50-I/SO

功能描述:8位微控制器 -MCU Full Spd USB 64KB Flsh 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J50-I/SP

功能描述:8位微控制器 -MCU Full Spd USB 64KB Flsh 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J50-I/SS

功能描述:8位微控制器 -MCU Full Spd USB 64KB Flsh 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J50T-I/ML

功能描述:8位微控制器 -MCU Full Spd USB 64KB Flsh 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J50T-I/SO

功能描述:8位微控制器 -MCU Full Spd USB 64KB Flsh 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J50T-I/SS

功能描述:8位微控制器 -MCU Full Spd USB 64KB Flsh 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J53-I/ML

功能描述:8位微控制器 -MCU 64KB 4KBRAM 12MIPS nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J53-I/SO

功能描述:8位微控制器 -MCU 64KB Flash 4KB RAM 12MIPS nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT